# Systèmes électroniques

Chapitre 2a

APPLICATION:

AMPLIFICATEUR DE PUISSANCE CLASSE AB

Dimensionnement

## $T A B L E \quad D E S \quad M A T I E R E S$

|    |       |                                                              | <u>PAGE</u> |

|----|-------|--------------------------------------------------------------|-------------|

| 2. | AMP   | LIFICATEUR DE PUISSANCE                                      | 5           |

|    | 2.1   | Préparation au laboratoire                                   | 5           |

|    | 2.1.1 | Dimensionnement d'un amplificateur audio classe AB.          | 5           |

|    | 2.2   | CAPACITÉ DE COMPENSATION C.                                  | 31          |

|    | 2.2.1 | Introduction                                                 | 31          |

|    | 2.2.2 | Modification de l'impédance d'entrée de l'étage différentiel | 31          |

|    | 2 2   | CONCLUSION                                                   | 22          |

## 2. AMPLIFICATEUR DE PUISSANCE.

#### 2.1 Préparation au Laboratoire

## 2.1.1 Dimensionnement d'un amplificateur audio classe AB.

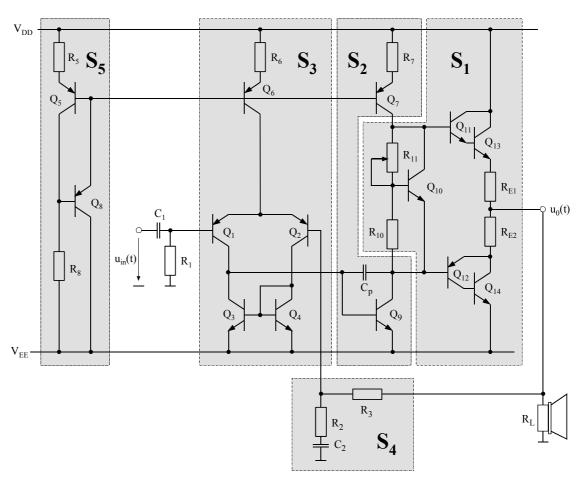

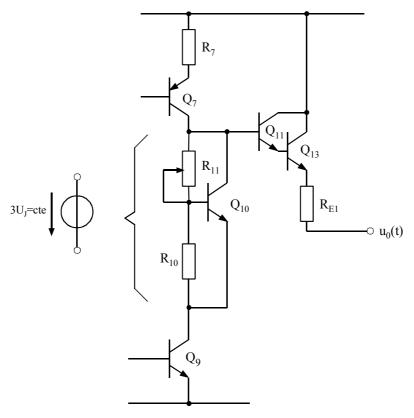

Soit l'amplificateur audio illustré à la Figure 2-1 présentant les caractéristiques suivantes

Puissance "efficace" de sortie : 12W sur une charge de  $6.8\Omega$  (haut parleur)

Gain en tension en boucle ouverte  $A_{V0}$  : >95dB

Gain en tension en boucle fermée  $A_{VF}$  : entre 20dB et 25dB

Impédance d'entrée :  $15k\Omega\pm10\%$

Bande passante :  $f_{min} \le 50 Hz$ ;  $f_{max} \ge 20 kHz$

Figure 2-1: Amplificateur Classe AB

## Les transistors à disposition sont :

| Modèle | Type | U <sub>Cemax</sub> [V] | I <sub>Cmax</sub> [mA] | P <sub>max</sub> [W] | $eta_{	ext{typ}}$ | U <sub>a</sub> [V] |

|--------|------|------------------------|------------------------|----------------------|-------------------|--------------------|

| PN100A | NPN  | 45                     | 500                    | 0.65                 | 150               | 120                |

| PN200A | PNP  | 45                     | 500                    | 0.65                 | 150               | 120                |

| 2N5191 | NPN  | 60                     | 4000                   | 40                   | 50                | 100                |

Note : U<sub>a</sub> représente la tension de Early

#### On demande:

- 1. D'expliquer le rôle de chaque bloc (S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>, S<sub>4</sub>, S<sub>5</sub>), plus particulièrement le rôle de Q<sub>10</sub>, P, R<sub>10</sub> dans le bloc S<sub>1</sub>, ainsi que celui de chaque résistance et chaque capacité du circuit.

- 2. De déterminer les tensions d'alimentation nécessaires (on propose une chute de tension au repos de 0.5V aux bornes de  $R_7$  et un courant de polarisation maximum de  $I_0$ =100mA pour le montage push-pull).

- 3. De dimensionner complètement le circuit (sauf C<sub>p</sub> : capacité pour la compensation en fréquence qui sera déterminée par simulation) en justifiant les choix, c'est-à-dire le type de chaque transistor en fonction de la puissance à dissiper, de la tension et du courant dans le pire cas d'utilisation.

- 4. De calculer le niveau DC (point de repos) en chaque nœud du circuit.

- 5. Calculer les gains en tension  $A_{V0}$  et  $A_{VF}$  dans la bande passante.

- 6. De calculer l'impédance d'entrée et de sortie

#### Remarques:

On admet les valeurs suivantes :

Tension Collecteur – Émetteur minimum :  $U_{CEMIN}=0.7V > U_{CEsat}$

#### 1. DÉFINITION DES BLOCS UTILISÉS.

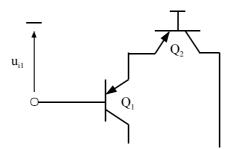

S1: Correspond à l'étage de puissance "Push-Pull" (gain en tension  $A_{V10}\cong 1$ ) réalisé à l'aide d'un montage Darlington pour réaliser la fonction NPN et d'un montage Pseudo-Darlington pour la fonction PNP. Le bloc constitué de  $Q_{10}$ ,  $R_{11}$  et  $R_{10}$  (multiplicateur de tension de jonction) permet la polarisation fine du courant dans l'étage push-pull des sorties en accord avec les résistances  $R_{E1}$  et  $R_{E2}$  et les 3 tensions de jonctions correspondant aux transistors  $Q_{11}$ ,  $Q_{12}$ ,  $Q_{13}$ . Ce multiplicateur de tension de jonction se comporte comme une source de tension continue.

Les résistances  $R_{E1}$  et  $R_{E2}$  évitent l'emballement thermique des transistors  $Q_{11}$ ,  $Q_{12}$ ,  $Q_{13}$ . La valeur de ces résistances se détermine de manière empirique en posant  $R_{E1}$ = $R_{E2}$ = $0.1R_L$

S2: Correspond à l'étage driver constitué d'une structure d'amplificateur de classe A à émetteur commun avec charge active sous la forme d'une source de courant ( $R_7$ ,  $Q_7$ ). (gain en tension  $A_{V20}$  <<1). La polarisation de la base de  $Q_9$  est assurée par la réaction négative globale. Pour éviter tout emballement thermique, il est possible d'ajouter une résistance dans l'émetteur avec un condensateur de forte valeur en parallèle pour court-circuiter la résistance du point de vue des petits signaux.

La charge active est réalisée au moyen d'un miroir de courant dégénéré (résistance dans l'émetteur). De cette manière on améliore sa précision et sa stabilité en température. En effet la tension Collecteur – Emetteur  $U_{CEQ7}$  du transistor  $Q_7$  est beaucoup plus grande que celle de  $Q_5$  et par conséquent  $Q_7$  dissipe une puissance plus grande et voit donc sa température de jonction plus élevée que celle de  $Q_5$ . Avec une tension de polarisation de 0.5V aux bornes de  $R_7$ , on garantit une erreur de courant inférieure à 10% pour une différence de température de 25°C entre les jonctions de  $Q_5$  et  $Q_7$  (rappel  $\Delta u_{BE} \approx -2 \text{mV/°C}$ , soit -50 mV pour  $\Delta T_J = 25$ °C, ce qui représente 10% des 0.5V).

La capacité C<sub>P</sub> est une capacité de compensation permettant d'assurer la stabilité en fréquence du circuit. Son implantation entre l'entrée et la sortie du driver permet de profiter de l'effet Miller.

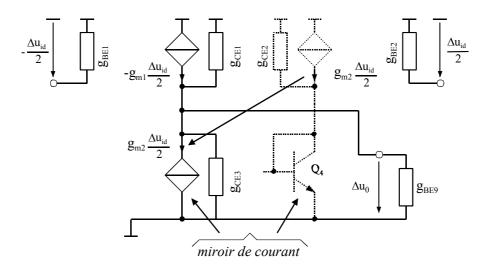

- S3: Correspond à l'étage d'entrée. Il s'agit d'un étage différentiel avec charge active (gain en tension A<sub>V30</sub>>>1). La structure différentielle de cet étage permet d'appliquer une réaction négative globale au circuit. L'étage est polarisé par un miroir de courant dégénéré constitué de Q<sub>5</sub>; R<sub>5</sub> et Q<sub>6</sub>; R<sub>6</sub> dont le fonctionnement est identique à celui décrit dans le bloc S2.

- S4: Correspond au circuit de contre-réaction de l'amplificateur de puissance (réaction négative globale). Ce circuit permet de contrôler précisément le gain en boucle fermée du circuit et d'améliorer fortement le taux de distorsion. Les valeurs des résistances R<sub>2</sub> et R<sub>3</sub> déterminent le gain en boucle fermée. La capacité C<sub>2</sub> provoque un gain unitaire en DC, ce qui permet de bien contrôler le point de repos et d'éliminer tout risque d'emballement thermique

- S5 : Correspond à la polarisation de la source de courant de référence utilisée pour les miroirs de courant. Il est à remarquer que le courant de polarisation de cette source de courant est dépendant de la tension d'alimentation

#### 2. DÉFINITION DES TENSIONS D'ALIMENTATION

Les tensions d'alimentation se déterminent en fonction de l'excursion de la tension de sortie du push-pull. Dans notre cas cette excursion se détermine en fonction de la charge et de la puissance à transmettre à celle-ci. La puissance efficace maximale définie dans la donnée correspond à la puissance moyenne maximale fournie à la charge en régime sinusoïdal.

$$V_{DD} = U_{o_{\text{max}}} + U_{RE1_{\text{max}}} + U_{BE(O13)} + U_{BE(O11)} + U_{CE(O7)_{\text{min}}} + U_{R7}$$

2.1

La tension de sortie maximale est définie par la puissance maximale à fournir à la charge

$$U_{o_{\text{max}}} = \sqrt{2 \cdot R_L \cdot P_{0_{\text{max}}}}$$

2.2

Comme on l'a vu, les résistances d'émetteurs  $R_{E1}$  et  $R_{E2}$  sont, de manière empirique, fixées à environ  $0.1R_L$ . La chute de tension aux bornes de  $R_{E1}$ , dans les conditions ou la tension de sortie correspond à la tension maximale de l'alternance positive :

$$U_{RE1_{\text{max}}} = I_{L_{\text{max}}} \cdot R_{E1} = \frac{U_{0_{\text{max}}}}{R_{L}} \cdot R_{E1}$$

2.3

Les tensions  $U_{BE(Q11)}$  et  $U_{BE(Q13)}$  sont fixées à 0.7V en régime normal de conduction. Si l'on veut éviter la saturation de  $Q_7$ , la tension  $U_{CE(Q7)}$  minimum doit être de l'ordre de 0.7V. Comme il a été précisé dans la donnée, la chute de tension aux bornes de la résistance  $R_7$  est constante (miroir de courant dégénéré) et vaut 0.5V.

On a donc en main tous les éléments nécessaires pour déterminer les tensions d'alimentation.

$$U_{a_{\text{max}}} = \sqrt{2 \cdot 6.8 \cdot 12} = \sqrt{163.2} = 12.8V$$

2.4

$$R_{E1} = 0.1 \cdot 6.8 = 0.68\Omega \tag{2.5}$$

En grandeur normalisée, on prendra

$$R_{E1} = 0.82\Omega$$

$$U_{RE1} = \frac{12.8}{6.8} \cdot 0.82 = 1.5V$$

2.6

$$V_{DD} = 12.8 + 1.5 + 0.7 + 0.7 + 0.7 + 0.5 = 16.9V$$

2.7

Vérifions que cette tension d'alimentation est suffisante pour une tension de sortie correspondant au maximum de l'alternance négative

$$V_{EE} = -U_{o_{\text{max}}} - U_{RE1_{\text{max}}} - U_{BE(Q12)} - U_{CE(Q9)_{\text{min}}}$$

2.8

pour les mêmes raisons que pour  $Q_7$ , la tension  $U_{CE(Q9)}$  minimum doit être de l'ordre de 0.7V

$$V_{EE} = -12.8 - 1.5 - 0.7 - 0.7 = -15.7V$$

2.9

Le choix de V<sub>DD</sub> et V<sub>EE</sub> peut donc être fixé à

$$V_{DD} = -V_{EE} = 17.0V$$

#### 3. DIMENSIONNEMENT DES ÉLÉMENTS DE L'AMPLIFICATEUR

#### 3.1 Bloc S1

Pour définir le type de transistor à utiliser, il est nécessaire de connaître les paramètres suivants :

- La tension maximum Collecteur Émetteur pour les transistors PNP ou la tension maximum Émetteur – Collecteur pour les transistors NPN

- Le courant maximum de Collecteur

- La puissance maximum dissipée (pire cas)

## 1.1.1 Transistor $Q_{13}$

La tension maximum  $U_{CEmax}$  correspond au maximum en valeur absolue de l'alternance négative de la tension de sortie

$$U_{CE(Q13)_{\text{max}}} = V_{DD} + |U_{0\text{max}}| = 17 + 12.8 = 29.8V$$

2.10

Le courant maximum  $I_{C(Q13)max}$  de collecteur correspond au maximum de l'alternance positive de la tension de sortie

$$I_{C(Q_{13})_{\text{max}}} = \frac{U_{0_{\text{max}}}}{R_L} = \frac{12.8}{6.8} = 1.9A.$$

2.11

La puissance maximum instantanée dissipée par le transistor ne correspond pas au produit de la tension  $U_{CE(Q13)max}$  par le courant  $I_{C(Q13)max}$ . En effet, lorsque la tension  $U_{CE(Q13)}$  est maximum, le courant  $I_{C(Q13)}$  est nul. Il s'agit de trouver ce maximum.

Pour l'alternance positive de la tension de sortie

$$p_{(Q13)}(t) = u_{CE(Q13)}(t) \cdot i_{CE(Q13)}(t)$$

$$= (V_{DD} - U_{0_{\text{max}}} \cdot \sin(\omega t)) \cdot \frac{U_{0_{\text{max}}}}{R_L} \cdot \sin(\omega t)$$

$$= U_{0_{\text{max}}} \cdot \frac{V_{DD}}{R_L} \cdot \sin(\omega t) - \frac{(U_{0_{\text{max}}})^2}{R_L} \cdot \sin^2(\omega t)$$

2.12

$$\frac{\partial(p_{Q3_{\text{max}}})}{\partial t} = U_{0_{\text{max}}} \cdot \frac{V_{DD}}{R_L} \omega \cdot \cos(\omega t) - \frac{(U_{0_{\text{max}}})^2}{R_L} \omega \cdot 2 \cdot \cos(\omega t) \cdot \sin(\omega t) = 0$$

$$\Rightarrow \frac{V_{CC}}{R_L} = 2 \cdot \frac{U_{0_{\text{max}}}}{R_L} \cdot \sin(\omega t)$$

$$\Rightarrow \sin(\omega t) = \frac{V_{DD}}{R_L} \cdot \frac{R_L}{2 \cdot U_{0_{\text{max}}}}$$

2.13

et finalement pour la puissance maximale instantanée

$$p_{(Q13)_{\text{max}}} = \frac{V_{DD}^2}{4 \cdot R_I}$$

2.14

$$p_{(Q^{13})_{\text{max}}} = \frac{17^2}{4 \cdot 6.8} = 10.6W$$

2.15

En résumé, les paramètres contraignants pour Q<sub>13</sub> sont les suivants

## 1.1.2 Transistor Q<sub>14</sub>

Les paramètres contraignants de Q<sub>14</sub> sont les mêmes que pour Q<sub>13</sub>, par conséquent

$$\begin{array}{c} U_{CE(Q14)_{\rm max}} = 29.8V \\ I_{C(Q14)_{\rm max}} = 1.9A \\ P_{(Q14)_{\rm max}} = 10.6W \end{array} \Rightarrow \begin{array}{c} Q_{14}: 2N5191 \\ Q_{15}: Q$$

## 1.1.3 Transistor $Q_{11}$

Le transistor  $Q_{11}$  voit sa tension Collecteur – Émetteur  $U_{CE(Q11)}$  suivre la tension Collecteur – Émetteur  $U_{CE(Q13)}$

$$U_{CE(Q11)} = U_{CE(Q13)} - U_{BE(Q13)} = 29.8 - 0.7 = 29.1V$$

2.16

Le courant de collecteur de Q<sub>11</sub> n'est rien d'autre que le courant de base de Q<sub>13</sub>

$$I_{C(Q11)} = I_{B(Q13)} = \frac{I_{C(Q13)}}{\beta_{(Q13)}} = \frac{1.9}{50} = 38mA$$

2.17

La puissance instantanée est définie comme

$$p_{(Q11)}(t) = i_{C(Q11)}(t) \cdot u_{CE(Q11)}(t) = \frac{i_{C(Q13)}(t)}{\beta_{(Q13)}} \cdot (u_{CE(Q13)}(t) - U_{BE(Q13)})$$

2.18

en première approximation on peut dire que la puissance instantanée maximum sera inférieure à

$$p_{(Q_{11})_{\text{max}}} < \frac{\left[i_{C(Q_{13})}(t) \cdot u_{CE(Q_{13})}(t)\right]_{\text{max}}}{\beta_{(Q_{13})}} = \frac{p_{(Q_{13})_{\text{max}}}}{\beta_{(Q_{13})}} = \frac{10.6}{50} = 212mW$$

2.19

En résumé, les paramètres contraignants pour Q<sub>11</sub> sont les suivants

$$\begin{array}{c} U_{CE(Q11)_{\rm max}} = 29.1 V \\ I_{C(Q11)_{\rm max}} = 38 mA \\ p_{(Q11)_{\rm max}} = 212 mW \end{array} \Rightarrow \begin{array}{c} Q_{11}: {\rm PN100A} \\ \end{array} \end{array} \right\} \begin{array}{c} \begin{array}{c} U_{\rm CEmax} : 45 V \\ I_{\rm Cmax} : 500 {\rm mA} \\ P_{\rm max} : 650 {\rm mW} \\ \beta_{\rm typ} : 150 \\ U_{\rm a} : 120 \end{array}$$

## 1.1.4 Transistor Q<sub>12</sub>

Le transistor  $Q_{12}$  présente les mêmes contraintes que  $Q_{11}$ . Seul le type est différent

## 1.1.5 Courants de base des transistors $Q_{11}$ et $Q_{12}$

Les valeurs maximales des courants de bases des transistors  $Q_{11}$  et  $Q_{12}$  peuvent être déterminées à l'aide des courants de collecteurs et les paramètres (gain en courant) des transistors sélectionnés

$$I_{B(Q11)_{\text{max}}} = \frac{i_{C(Q11)_{\text{max}}}}{\beta_{(Q11)}} = \frac{38}{150} = 0.25 mA$$

2.20

$$I_{B(Q_{12})_{\text{max}}} = \frac{i_{C(Q_{12})_{\text{max}}}}{\beta_{(Q_{12})}} = \frac{38}{150} = 0.25 \text{mA}$$

2.21

C'est le bloc S2 qui doit être capable de fournir le courant  $I_{B(Q11)max}$  lors des alternances positives et absorber le courant  $I_{B(Q12)max}$  lors des alternances négatives. La limitation du courant en absorption n'est limitée que par le courant de saturation de  $Q_9$ . Par contre le courant maximum que peut fournir le bloc S2 correspond au courant circulant dans le miroir de courant  $(Q_7, R_7)$ . Ce courant doit donc être supérieur ou égal au courant  $I_{B(Q11)max}$ . Un courant trop important dans  $Q_7$  provoque un échauffement de ce dernier risquant de modifier sensiblement le courant du miroir par rapport au courant de référence circulant dans le

transistor  $Q_5$ . En effet si les courants circulant dans  $Q_5$  et  $Q_7$  sont égaux, la tension  $U_{CE(Q5)}$  étant égale à la somme de la tension  $U_{BE(Q5)}$  et  $U_{BE(Q8)}$  soit environ 1.4V est nettement inférieure à la tension  $U_{CE(Q5)}$ . De plus, un courant  $I_{C(Q7)}$  trop proche du courant  $I_{B(Q11)}$  amène le transistor  $Q_9$  proche du blocage avec les risques de distorsion qui en résulteraient. En pratique, il faut faire un compromis en distorsion et dissipation de puissance. Le courant dans le miroir est fixé à une valeur correspondant à 20 fois le courant maximum de base de  $Q_{11}$ .

$$I_{C(Q7)} = 20 \cdot I_{B(Q11)_{\text{max}}} = 20 \cdot 0.25 = 5mA$$

2.22

## 1.1.6 Multiplicateur de tension de jonction ( $Q_{10}$ , $R_{10}$ , $R_{11}$ )

Ce multiplicateur de tension permet de créer une source de tension constante légèrement supérieure à la somme des tensions Base – Émetteur de  $Q_{11}$ ,  $Q_{12}$ ,  $Q_{13}$ . En négligeant le courant de base de  $Q_{10}$ , on peut écrire

$$U_{CE(Q10)} = \frac{R_{10} + R_{11}}{R_{10}} \cdot U_{BE(Q10)}$$

2.23

Le courant de polarisation (repos) circulant dans les transistors de sortie ( $Q_{13}$  et  $Q_{14}$ ) est défini comme

$$I_{0(Q13,Q14)} = \frac{U_{CE(Q10)} - U_{BE(Q11)} - U_{BE(Q13)} - U_{BE(Q12)}}{R_{E1} + R_{E2}}$$

2.24

En choisissant le courant de polarisation  $I_{0(Q13,Q14)}$  à une valeur maximum de 80mA, on peut calculer  $U_{CE(Q10)}$  maximum

$$U_{CE(Q10)} = I_{0(Q13,Q14)} \cdot (R_{E1} + R_{E2}) + U_{BE(Q11)} + U_{BE(Q13)} + U_{BE(Q12)}$$

= 0.08 \cdot (0.82 + 0.82) + 0.7 + 0.7 + 0.7 = 2.23V

Le courant circulant dans le multiplicateur de courant est compris entre

$$I_{C(Q7)} - I_{B(Q11) \max} \Big|_{\substack{Alternance \\ positive}} \le I_{MULT} \le I_{C(Q7)} \Big|_{\substack{Alternance \\ négative}}$$

2.26

Pour qu'un courant circule dans le transistor  $Q_{10}$ , il faut que lors d'une alternance positive, le courant circulant dans  $R_{10}$  et  $R_{11}$  soit inférieur à  $I_{MULTmin} = 4.75 mA$ . En admettant dans ce cas une répartition du courant de  $\{1/5; 4/5\}$ , soit environ 1 mA dans  $R_{11}$ ,  $R_{10}$  et le reste dans le transistor  $Q_{10}$ , on obtient :

$$R_{10} = \frac{5 \cdot U_{BE(Q10)}}{(I_{C(Q7)} - I_{B(Q11)_{max}})} = \frac{5 \cdot 0.7}{(5 - 0.25) \cdot 10^{-3}} = 737\Omega$$

2.27

$$R_{10} = 1k\Omega$$

et par conséquent

$$R_{11} = \left(\frac{U_{CE(Q10)}}{U_{BE(O10)}} - 1\right) \cdot R_{10} = \left(\frac{2.23}{0.7} - 1\right) \cdot 1000 = 2186\Omega$$

2.28

$$R_{11} = 2k\Omega$$

La tension  $U_{CE(Q10)}$  et le courant  $I_{C(Q10)}$  maximum sont faibles et par conséquent ne sont pas contraignants pour le transistor. Il en va de même pour la puissance dissipée.

$$I_{C(Q_{10})_{\text{max}}} = I_{C(Q_{7})} - I_{(P_{1})} = I_{C(Q_{7})} - \frac{1}{5} \cdot (I_{C(Q_{7})} - I_{B(Q_{11})_{\text{max}}})$$

$$= \frac{1}{5} \cdot (4 \cdot I_{C(Q_{7})} + I_{B(Q_{11})_{\text{max}}}) = \frac{1}{5} \cdot (4 \cdot 5 + 0.25) = 5mA$$

2.29

$$P_{(Q10)_{\text{max}}} = I_{C(Q10)_{\text{max}}} \cdot U_{CE(Q10)} = 4 \cdot 2.26 = 9mW$$

2.30

En résumé, on a pour le transistor  $Q_{10}$  du multiplicateur de tension :

#### 1.2 Bloc S2

## 1.2.1 Miroir de courant dégénéré ( $Q_7$ , $R_7$ )

Selon la donnée, la chute de tension aux bornes de  $R_7$  est fixée à 0.5V, le courant étant constant  $I_{C(O7)} = 5$ mA. La résistance  $R_7$  vaut donc

$$R_7 = \frac{U_{R7}}{I_{C(O7)}} = \frac{0.5}{5 \cdot 10^{-3}} = 100\Omega$$

2.31

$$R_7 = 100\Omega$$

La tension Émetteur – Collecteur  $U_{EC(Q7)}$  du transistor  $Q_7$  est maximum lorsque la tension de sortie est minimum (alternance négative), soit  $-U_{0max}$ .

$$U_{EC(Q7)_{\text{max}}} = V_{DD} - (U_{BE(Q11)} + U_{BE(Q13)} + U_{R7} - U_{0_{\text{max}}})$$

$$= 17 - (0.7 + 0.7 + 0.5 - 12.8) = 27.9V$$

2.32

La puissance maximum dissipée par  $Q_7$  est directement liée à la tension Émetteur – Collecteur  $U_{EC(O7)max}$

$$P_{(Q^7)_{\text{max}}} = I_{C(Q^7)} \cdot U_{EC(Q^7)_{\text{max}}} = 5 \cdot 27.9 = 140 \text{mW}$$

2.33

En résumé, les paramètres contraignants pour Q<sub>7</sub> sont les suivants

## 1.2.2 Émetteur commun Q9

La tension Collecteur - Émetteur  $U_{CE(Q9)}$  du transistor  $Q_9$  est maximum lorsque la tension de sortie est maximum (alternance positive), soit  $+U_{0max}$ .

$$U_{CE(Q9)_{\text{max}}} = U_{0_{\text{max}}} - (U_{BE(Q12)} + V_{EE})$$

= 12.8 - (0.7 - 17) = 29.1V

Le courant de collecteur maximum de  $I_{C(Q9)max}$  est la somme du courant de provenant du miroir dégénéré  $(Q_7, R_7)$  et du courant de base maximum soutiré au transistor  $Q_{12}$ .

$$I_{C(Q9)_{\text{max}}} = I_{C(Q7)} + I_{B(Q12)_{\text{max}}} = 5 + 0.25 = 5.25 \text{mA}$$

2.35

La puissance maximum dissipée par  $Q_9$  n'est pas le produit de la tension  $U_{CE(Q9)max}$  par le courant  $I_{C(Q9)max}$ , ces maximas n'étant pas présents en même temps.

$$\begin{split} p_{(Q^{9})}(t) &= u_{EC(Q^{9})}(t) \cdot i_{C(Q^{9})}(t) \\ &= (U_{EC^{0}(Q^{9})} + \hat{U}_{EC(Q^{9})} \cdot \sin(\omega \cdot t)) \cdot (I_{C^{0}(Q^{9})} - \hat{I}_{C(Q^{9})} \cdot \sin(\omega \cdot t)) \\ &= U_{EC^{0}(Q^{9})} \cdot I_{C^{0}(Q^{9})} \\ &+ (\hat{U}_{EC(Q^{9})} \cdot I_{C^{0}(Q^{9})} - U_{EC^{0}(Q^{9})} \cdot \hat{I}_{C(Q^{9})}) \cdot \sin(\omega \cdot t) \\ &- (\hat{U}_{EC(Q^{9})} \cdot \hat{I}_{C(Q^{9})}) \cdot \sin^{2}(\omega \cdot t) \end{split}$$

il s'agit de trouver le maximum de la puissance pulsante  $p_{AC}(t)$

$$p_{AC(Q^{9})}(t) = (\hat{U}_{EC(Q^{9})} \cdot I_{C0(Q^{9})} - U_{EC0(Q^{9})} \cdot \hat{I}_{C(Q^{9})}) \cdot \sin(\omega \cdot t) - (\hat{U}_{EC(Q^{9})} \cdot \hat{I}_{C(Q^{9})}) \cdot \sin^{2}(\omega \cdot t)$$

2.37

$$\begin{split} \frac{\partial (p_{AC(Q^9)_{\text{max}}})}{\partial t} &= (\hat{U}_{EC(Q^9)} \cdot I_{C0(Q^9)} - U_{EC0(Q^9)} \cdot \hat{I}_{C(Q^9)}) \cdot \omega \cdot \cos(\omega \cdot t) \\ &- 2 \cdot (\hat{U}_{EC(Q^9)} \cdot \hat{I}_{C(Q^9)}) \cdot \omega \cdot \sin(\omega \cdot t) \cdot \cos(\omega \cdot t) = 0 \end{split}$$

2.38

$$\begin{split} &\Rightarrow (\hat{U}_{EC(Q9)} \cdot I_{C0(Q9)} - U_{EC0(Q9)} \cdot \hat{I}_{C(Q9)}) - 2 \cdot (\hat{U}_{EC(Q9)} \cdot \hat{I}_{C(Q9)}) \cdot \sin(\omega \cdot t) \\ &\Rightarrow \sin(\omega \cdot t) = \frac{\hat{U}_{EC(Q9)} \cdot I_{C0(Q9)} - U_{EC0(Q9)} \cdot \hat{I}_{C(Q9)}}{2 \cdot (\hat{U}_{EC(Q9)} \cdot \hat{I}_{C(Q9)})} \end{split}$$

et finalement pour la puissance instantanée maximale pulsante

$$p_{AC(Q^9)_{\text{max}}} = \frac{\left(\hat{U}_{EC(Q^9)} \cdot I_{C0(Q^9)} - U_{EC0(Q^9)} \cdot \hat{I}_{C(Q^9)}\right)^2}{4 \cdot (\hat{U}_{EC(Q^9)} \cdot \hat{I}_{C(Q^9)})}$$

2.39

Avec

$$\begin{split} U_{EC0(Q9)} &= -V_{EE} - U_{BE(Q12)} - R_{E2} \cdot I_0 = 17 - 0.7 - 0.82 \cdot 0.08 = 16.2V \\ I_{C0(Q9)} &= I_{C(Q7)} = 5mA \\ \hat{U}_{EC(Q9)} &\cong \hat{U}_{0\max} = 12.8V \\ \hat{I}_{C(Q9)} &= I_{B(Q11,Q12)} = 0.25mA \end{split}$$

$$p_{(Q^{9})_{\text{max}}} = p_{DC(Q^{9})} + p_{AC(Q^{9})_{\text{max}}}$$

$$= U_{EC0(Q^{9})} \cdot I_{C0(Q^{9})} + \frac{\left(\hat{U}_{EC(Q^{9})} \cdot I_{C0(Q^{9})} - U_{EC0(Q^{9})} \cdot \hat{I}_{C(Q^{9})}\right)^{2}}{4 \cdot (\hat{U}_{EC(Q^{9})} \cdot \hat{I}_{C(Q^{9})})}$$

$$= 16.2 \cdot 5 \cdot 10^{-3} + \frac{\left(12.8 \cdot 5 \cdot 10^{-3} - 16.2 \cdot 0.25 \cdot 10^{-3}\right)^{2}}{4 \cdot (12.8 \cdot 0.25 \cdot 10^{-3})} = 362mW$$

2.41

En résumé, les paramètres contraignants pour Q<sub>9</sub> sont les suivants

Le courant de base maximum de Q<sub>9</sub> est défini comme

$$I_{B(Q^9)_{\text{max}}} = \frac{I_{C(Q^9)_{\text{max}}}}{\beta_{(Q^9)}} = \frac{5.25}{150} = 35\mu A$$

2.42

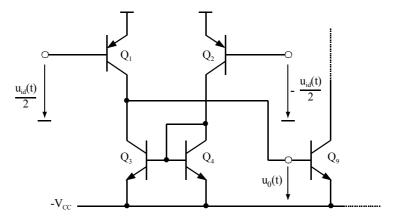

#### 1.3 Bloc S3

## 1.3.1 Miroir de courant dégénéré ( $Q_6$ , $R_6$ )

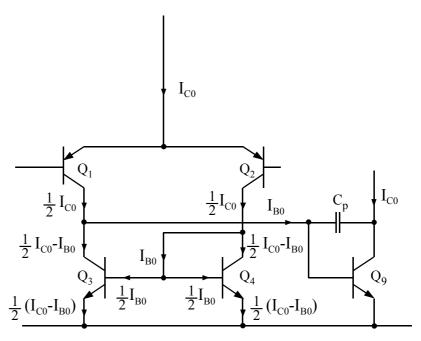

La sortie de l'étage S3 doit être capable de fournir le courant d'entrée de l'étage driver (Bloc S2). De plus, afin de limiter l'offset de l'amplificateur complet, il serait judicieux qu'au repos, le courant de base  $I_{B(Q9)}$  du transistor  $Q_9$  soutiré à la branche de gauche soit compensé par le courant de base de  $Q_3$  et  $Q_4$ . En choisissant des transistors identiques pour  $Q_3$ ,  $Q_4$ ,  $Q_9$ , on peut écrire

$$I_{C0(Q3)} = I_{C0(Q4)} = \frac{1}{2} \cdot I_{C0(Q9)}$$

2.43

et pour le courant de collecteur du miroir dégénéré (Q<sub>6</sub>, R<sub>6</sub>) on obtient

$$I_{C0(Q6)} = I_{C0(Q9)} = I_{C0(Q7)} = 5mA$$

2.44

La Figure 2-2 montre la répartition des courants pour le cas défini ci-dessus

Figure 2-2 : Montage différentiel d'entrée

Le choix de I<sub>C(O6)</sub> impose pour la résistance R<sub>6</sub> une valeur identique à celle de R<sub>7</sub>.

$$R_6 = 100\Omega$$

Le transistor  $Q_6$ , identique à  $Q_7$  permet un appariement des miroirs de courant. La tension Émetteur – Collecteur de  $Q_6$  maximum, en sachant que le gain en en boucle fermée est de 20dB au minimum ( $A_{VF}$ =10), vaut

$$U_{EC(Q6)_{\text{max}}} = V_{DD} - (U_{R6} + U_{BE(Q1,2)} - \frac{U_{0_{\text{max}}}}{A_{VF}})$$

$$= 17 - (0.5 + 0.7 - \frac{12.8}{10}) = 17.1V$$

2.45

La puissance instantanée maximale dissipée par ce transistor vaut donc

$$p_{(Q6)_{\text{max}}} = U_{EC(Q6)_{\text{max}}} \cdot I_{C(Q6)}$$

$$= 17.1 \cdot 5 = 86 mW$$

2.46

Le choix du transistor conduit à

| $U_{EC(OE)} = 17.1V$           |                                       | ) | $U_{CEmax}$    | : | 45V   |

|--------------------------------|---------------------------------------|---|----------------|---|-------|

| EC (Q6) max                    |                                       |   | $I_{Cmax}$     | : | 500mA |

| $I_{C(Q6)} = 5mA$              | $\Rightarrow$ Q <sub>6</sub> : PN200A | } | $P_{max}$      | : | 650mW |

| 0.5                            |                                       |   | $\beta_{typ}$  | : | 150   |

| $p_{(Q6)_{\text{max}}} = 86mW$ |                                       | , | U <sub>a</sub> | : | 120   |

## 1.3.2 Miroir de courant $(Q_3, Q_4)$

Les transistors du Q<sub>3</sub> et Q<sub>4</sub> du miroir de courant sont identiques à Q<sub>9</sub>.Leur tension Collecteur – Emetteur reste faible

$$\begin{split} U_{CE(Q3)_{\text{max}}} &= U_{BE(Q9)} = 0.7V \\ U_{CE(Q4)_{\text{max}}} &= U_{BE(Q4)} = 0.7V \end{split}$$

2.47

Les courants de collecteur maximums valent respectivement

$$I_{C(Q3)_{\text{max}}} \cong I_{C(Q4)_{\text{max}}} \cong \frac{1}{2} \cdot I_{C(Q6)} = 2.5 \text{mA}$$

2.48

Ainsi la puissance dissipée dans chacun des transistors est nettement inférieure à celle dissipée dans Q<sub>9</sub>.

$$P_{(Q_{3},Q_{4})_{\text{max}}} = U_{CE(Q_{3},Q_{4})_{\text{max}}} \cdot I_{C(Q_{3},Q_{4})_{\text{max}}} = 0.7 \cdot 2.5 = 1.75 mW$$

2.49

Le choix des transistors Q<sub>3</sub> et Q<sub>4</sub> conduit à

$$\begin{array}{c} U_{CE(Q3,Q4)_{\rm max}} = 0.7V \\ I_{C(Q3,Q4)_{\rm max}} = 2.5mA \\ p_{(Q3,Q4)_{\rm max}} = 1.75mW \end{array} \Rightarrow \begin{array}{c} Q_{3,4}: {\rm PN100A} \\ \end{array} \} \begin{array}{c} U_{\rm CEmax} : 45V \\ I_{\rm Cmax} : 500 {\rm mA} \\ P_{\rm max} : 650 {\rm mW} \\ \beta_{\rm typ} : 150 \\ U_{\rm a} : 120 \end{array}$$

## 1.3.3 Transistors de l'étage différentiel d'entrée $Q_1$ et $Q_2$

Les courants maximums de Collecteur  $I_{C(Q1)}$  et  $I_{C(Q2)}$  sont équivalents aux courants maximums de collecteurs des transistors  $I_{C(Q3)}$  et  $I_{C(Q4)}$

Les tensions maximums Émetteurs – Collecteurs Q<sub>3</sub> et Q<sub>4</sub> valent

$$U_{EC(Q_1)_{\text{max}}} \cong U_{EC(Q_2)_{\text{max}}} = -V_{EE} + \frac{U_{0_{\text{max}}}}{A_{VF}} + U_{BE(Q_2)} - U_{BE(Q_4)}$$

$$= 17 + \frac{12.8}{10} + 0.7 - 0.7 = 18.3V$$

2.50

Les puissances instantanées dissipées maximums prennent les valeurs

$$p_{(Q_1)_{\text{max}}} \cong p_{(Q_2)_{\text{max}}} = U_{EC(Q_1,2)_{\text{max}}} \cdot I_{C(Q_1,2)_{\text{max}}}$$

$$= 18 \ 3 \cdot 2 \ 5mA = 46mW$$

2.51

Ce qui nous amène au choix des transistors suivant

#### 1.4 Bloc S5

## 1.4.1 Transistors $Q_5$ et $Q_8$ et résistances de la référence de courant

C'est de ce bloc qu'est issu la source de courant de référence pour les miroirs dégénérés ( $T_6$ ,  $R_6$ ) et ( $T_7$ ,  $R_7$ ). Pour des raisons appariement, le transistor  $Q_5$  doit être identique aux transistors  $Q_6$  et  $Q_7$ . En choisissant  $R_5$  identique à  $R_6$  et  $R_7$  on fixe le courant de collecteur  $I_{C(Q_5)}$  égal aux courants  $I_{C(Q_6)}$  et  $I_{C(Q_7)}$ . La tension Émetteur – Collecteur  $U_{EC(Q_5)}$  est constante. En résumé, on peut écrire

$$R_5 = R_6 = R_7 = 100\Omega$$

$$I_{C(Q5)} = I_{C(Q6)} = I_{C(Q7)} = 5mA$$

2.52

$$U_{EC(OS)} = U_{EB(OS)} + U_{EB(OS)} = 0.7 + 0.7 = 1.4V$$

2.53

$$P_{(O5)} = U_{EC(O5)} \cdot I_{C(O5)} = 1.4 \cdot 5 = 7mW$$

2.54

Le transistor sélectionné correspond à

La tension aux bornes de R<sub>8</sub> se calcule aisément

$$U_{R8} = V_{DD} - V_{EE} - U_{R5} - U_{EB(Q5)} - U_{EB(Q8)} = 17 + 17 - 0.5 - 0.7 - 0.7 = 32.1V$$

2.55

Le courant dans R<sub>8</sub> étant défini, il est possible de calculer cette dernière

$$R_8 = \frac{U_{R8}}{I_{C(O5)}} = \frac{32.1}{5} = 6.42k\Omega$$

2.56

$$R_8 = 6.8k\Omega$$

Le courant circulant dans le collecteur de Q<sub>8</sub> est défini par

$$I_{C(Q8)} = I_{B(Q5)} + I_{B(Q6)} + I_{B(Q7)} = \frac{I_{C(Q5)}}{\beta_{(Q5)}} + \frac{I_{C(Q6)}}{\beta_{(Q6)}} + \frac{I_{C(Q7)}}{\beta_{(Q7)}}$$

$$= 3 \cdot \frac{5}{150} = 100 \,\mu A$$

2.57

La tension Émetteur – Collecteur de  $\mathrm{Q}_8$  vaut

$$U_{EC(Q8)} = 2 \cdot V_{CC} - U_{R5} - U_{EB(Q5)} = 2 \cdot 17 - 0.5 - 0.7 = 32.8V$$

2.58

et par conséquent la puissance dissipée par  $Q_8$

$$P_{Q8} = U_{EC(Q8)} \cdot I_{C(Q8)} = 32.8 \cdot 100 = 3.3 mW$$

2.59

On choisit Q<sub>8</sub> identique à Q<sub>5</sub> et par conséquent

| $ \begin{vmatrix} U_{CE(Q8)} = 32.8V \\ I_{C(Q8)} = 100 \mu\text{A} \\ p_{(Q8)} = 3.3 mW \end{vmatrix} \Rightarrow Q_8: \text{PN200A} $ $ \geqslant Q_8: \text{PN200A} $ $ \begin{vmatrix} U_{\text{CEmax}} & : & 45V \\ I_{\text{Cmax}} & : & 500 \text{mA} \\ P_{\text{max}} & : & 650 \text{mV} \\ \beta_{\text{typ}} & : & 150 \\ U_a & : & 120 \end{vmatrix} $ |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

## 4. POLARISATION

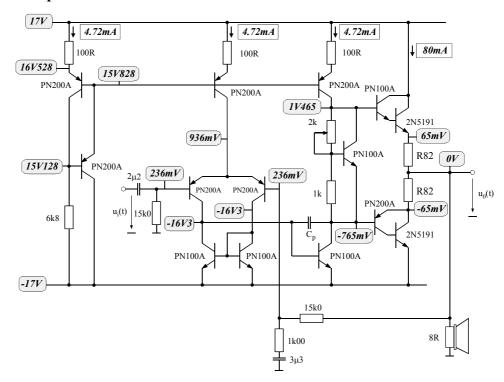

## 4.1 Tensions de polarisation

Figure 2-3: Amplificateur Classe AB: Tensions de polarisation

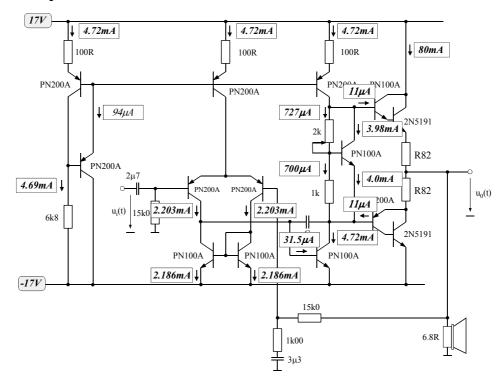

## 4.2 Courants de polarisation

Figure 2-4: Amplificateur Classe AB: Courants de polarisation

## 5. GAIN EN TENSION DANS LA BANDE PASSANTE.

## 5.1 Détermination du gain en boucle ouverte

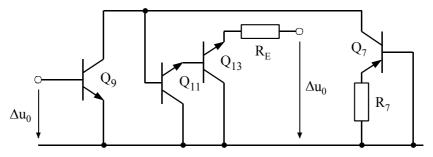

Le gain en boucle ouverte se calcule en deux temps. En effet on peut admettre en première approximation que le gain du push-pull vaut 1. Il reste donc à calculer le gain de l'étage driver S2 et le gain de l'étage différentiel S3

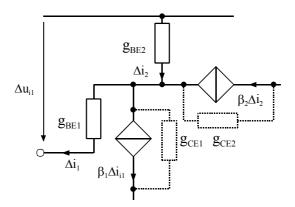

## 5.1.1 Gain de l'étage driver S2

Comme on l'a déjà mentionné, l'étage driver correspond à un amplificateur de classe A avec charge active. En faisant les hypothèses suivantes :

- le miroir de courant  $(Q_7, R_7)$  garde une tension constante aux bornes de  $R_7$

- le multiplicateur de tension est considéré comme parfait (source de tension continue)

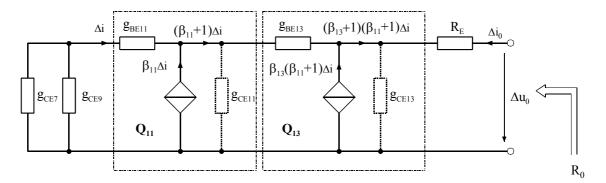

on peut esquisser le schéma pour accroissement de la Figure 2-7.

Figure 2-5: Etage driver et push pull (origine d'une alternance positive)

Figure 2-6 : Etage driver : Schéma petits signaux (origine d'une alternance positive)

Figure 2-7 : Etage driver : Schéma pour accroissement (origine d'une alternance positive)

Le gain en tension de cet étage est défini comme

$$A_{V2} = \frac{\Delta u_S}{\Delta u_i} = -g_{m9} \cdot (\frac{1}{g_{CE9}} //R_{is} // \frac{1}{g_{CE7}})$$

2.60

où  $R_{is}$  est l'impédance de charge de l'étage driver, soit l'impédance d'entrée de l'étage Push-Pull (charge  $R_L$  non connectée). En première approximation  $R_{is} \cong 1.3 M\Omega$

$$R_{iS} = \frac{\Delta u_S}{\Delta i_S} >> \frac{1}{g_{CE9}} // \frac{1}{g_{CE7}}$$

2.61

par conséquent

$$g_{m9} = \frac{I_{C0(Q7)}}{U_T} = \frac{4.72}{26} = 0.18 \, A/V$$

2.62

$$g_{CE7} = \frac{I_{C0(Q7)}}{U_{a(Q7)} + U_{CE0(Q7)}} = \frac{4.72}{120 + 15.5} = 35 \,\mu\text{A/V}$$

2.63

$$g_{CE9} = \frac{I_{C0(Q7)}}{U_{a(Q9)} + U_{CE0(Q9)}} = \frac{4.72}{120 + 17.8} = 34 \,\mu\text{A/V}$$

2.64

$$A_{V2} = \frac{\Delta u_S}{\Delta u_i} = -0.18 \cdot \frac{1}{35 \cdot 10^{-6} + 34 \cdot 10^{-6}} = -2608$$

(68*dB*)

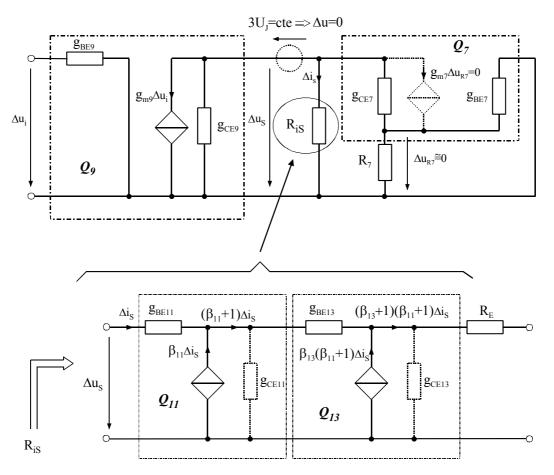

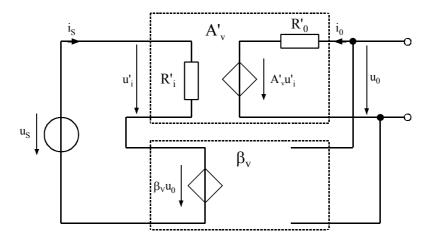

## 5.1.2 Gain de l'étage différentiel S3

Pour le calcul du gain différentiel, on fixe une tension d'entrée sans mode commun par rapport à la masse de référence (0V). La Figure 2-8 illustre la partie importante de cet étage. La charge de ce dernier n'est rien d'autre que l'étage driver représenté par Q<sub>9</sub>.

Figure 2-8 : Etage différentielle d'entrée

Vu la symétrie de la partie différentielle, on peut admettre que la tension d'émetteur de  $Q_1$  et  $Q_2$  se trouve au milieu de la différence de potentiel entre les bases de ces mêmes transistors. Il est donc possible de diviser le montage en deux parties. En tenant compte du miroir de courant qui impose que le courant dans  $Q_3$  soit identique au courant circulant dans  $Q_2$ , on obtient la topologie définie à la Figure 2-9.

Figure 2-9 : Etage différentiel : Schéma pour accroissement

Du schéma par accroissement, en négligeant g<sub>CE1</sub>, g<sub>CE2</sub> et g<sub>CE3</sub> on peut calculer le gain en tension de l'étage S3.

$$A_{V3} = \frac{\Delta u_0}{\Delta u_{id}} = -\frac{1}{g_{RF0}} \cdot (\frac{g_{m1} + g_{m2}}{2})$$

2.66

avec

$$\frac{1}{g_{BE9}} = \frac{\beta_9 \cdot U_T}{I_{C0(07)}} = \frac{150 \cdot 26}{4.72} = 826\Omega$$

2.67

$$g_{m1} = g_{m2} = \frac{I_{C0(Q6)}}{2 \cdot U_T} = \frac{4.72}{2 \cdot 26} = 91 \text{ mA/V}$$

2.68

ce qui donne pour le gain

$$A_{V3} = \frac{\Delta u_S}{\Delta u_{id}} = -826 \cdot 91 \cdot 10^{-3} = -75$$

(38dB) 2.69

## 5.1.3 Gain en boucle ouverte

Finalement le gain en boucle ouverte vaut

$$A_V = A_{V1} \cdot A_{V2} \cdot A_{V3} = 1 \cdot (-2806) \cdot (-75) = 210450$$

(106*dB*)

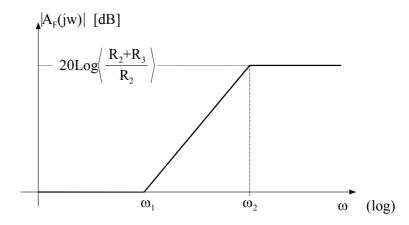

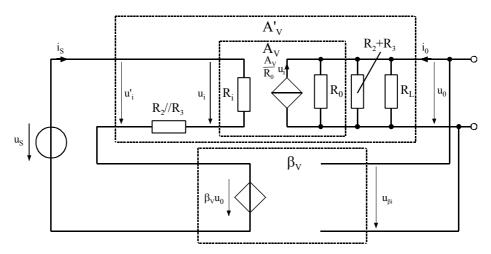

## 5.2 Circuit de réaction

Pour respecter les exigences de gain en boucle fermée (20-25 dB), le réseau de réaction est défini comme (valable pour de fréquence élevée, c'est-à-dire sans l'influence du condensateur  $C_2$ )

$$\beta_V = \frac{R_2}{R_2 + R_3} = 16$$

2.71

L'impédance d'entrée étant fixée à  $15k\Omega\pm10\%$ , on fixe R<sub>1</sub> à :

$$R_1 = 15k\Omega$$

Lorsque l'entrée est constante, la sortie de l'amplificateur est maintenue à 0V en raison de la capacité de découplage  $C_1$ . Afin d'éviter un offset, on fixe la résistance  $R_3$  égale à  $R_1$ , ceci afin de charge les entrées de l'étage différentiel de manière symétrique. En fixant la valeur de  $R_3$  on a également fixé la valeur de  $R_2$

$$R_3 = 15k\Omega$$

,  $R_2 = 1k\Omega$

En ne tenant pas compte du filtre passe haut réalisé par  $C_1$  et  $R_1$ , on a pour la fonction de transfert en boucle fermée

$$A_F(j\omega) = \frac{A_V}{1 + \beta_V(j\omega) \cdot A_V} \cong \frac{1}{\beta_V(j\omega)} = \frac{1 + j\omega \cdot C_2 \cdot (R_2 + R_3)}{1 + j\omega \cdot C_2 \cdot R_2}$$

2.72

Figure 2-10 Fonction de transfert en boucle fermée

On choisit la fréquence supérieure f<sub>2</sub> à 50Hz, ce qui donne pour C<sub>2</sub>

$$C_{2} = \frac{1}{2 \cdot \pi \cdot f_{2} \cdot R_{2}}$$

$$= \frac{1}{2 \cdot \pi \cdot 50 \cdot 1000} = 3.18 \mu F$$

$$C_{2} = 3.3 \mu F$$

2.73

La valeur normalisée de  $C_2$  donne 48Hz pour  $f_2$  et par conséquent  $f_1=f_2/16=3$ Hz

Pour finir, on choisit de placer le pôle défini par C<sub>1</sub> une décade en dessous de f<sub>2</sub>

$$C_{1} = \frac{10}{2 \cdot \pi \cdot f_{2} \cdot R_{1}}$$

$$= \frac{10}{2 \cdot \pi \cdot 50 \cdot 15000} = 2.12 \mu F$$

2.74

$C_1 = 2.2 \mu F$

## 5.3 Calcul des éléments du quadripôle A'v modifié

## 5.3.1 Impédance d'entrée de l'amplificateur

L'impédance d'entrée est définie entre la base de  $Q_1$  et la masse (l'entrée (-), base de  $Q_2$  étant mise à la masse). Vu la source de courant dans l'émetteur des transistors  $Q_1$  et  $Q_2$ , pour les

petits signaux  $Q_1$  se comporte comme un montage émetteur commun dégénéré par la présence d'une charge entre son émetteur et la masse. Cette charge n'est autre l'impédance d'entrée de  $Q_2$  monté en base commune. La Figure 2-11 illustre le schéma "petits signaux" utile pour cette entrée.

Figure 2-11 : Etage différentiel : Schéma petits signaux pour l'entrée

Le schéma pour accroissement issu du schéma petits signaux de la Figure 2-11 prend la forme suivante

Figure 2-12 : Etage différentiel : Schéma pour accroissement pour l'entrée

De la Figure 2-12, on peut en déduire la valeur de l'impédance d'entrée.

$$R_i = \frac{\Delta u_{i1}}{\Delta i_1}$$

2.75

La tension d'entrée est définie comme

$$\Delta u_{i1} = \frac{1}{g_{BE1}} \cdot \Delta i_1 + \frac{1}{g_{BE2}} \cdot \Delta i_2$$

2.76

La relation entre les courants prend la forme

$$(\beta_1 + 1) \cdot \Delta i_1 = (\beta_2 + 1) \cdot \Delta i_2$$

2.77

ce qui nous amène à la relation

$$\Delta u_{i1} = \frac{1}{g_{BE1}} \cdot \Delta i_1 + \frac{1}{g_{BE2}} \cdot \frac{\beta_1 + 1}{\beta_2 + 1} \Delta i_1$$

2.78

Les transistors  $Q_1$  et  $Q_2$  étant en principe appariés, on peut admettre que  $\beta_1 = \beta_2$  et  $g_{BE1} = g_{BE2}$ Finalement, on obtient pour l'impédance d'entrée

$$R_i = \frac{2}{g_{REI}}$$

2.79

avec

$$\frac{1}{g_{BE1}} = \frac{2 \cdot \beta_1 \cdot U_T}{I_{C0(O6)}} = \frac{2 \cdot 150 \cdot 26}{4.72} = 1652\Omega$$

2.80

et par conséquent

$$R_i = 3305\Omega ag{2.81}$$

## 5.3.2 Impédance de sortie de l'amplificateur

L'impédance de sortie est donnée pour une alternance positive, soit pour la conduction des transistors  $Q_{11}$  et  $Q_{13}$ . La Figure 2-13 illustre le schéma pour accroissement pour ce cas de fonctionnement

Figure 2-13 : Etage push-pull de sortie : Schéma pour accroissement

On peut écrire :

$$\Delta u_0 = -\left(\frac{1}{g_{CE7}} / / \frac{1}{g_{CE9}}\right) + \frac{1}{g_{BE11}} + (\beta_{11} + 1) \cdot \frac{1}{g_{BE13}} + (\beta_{11} + 1) \cdot (\beta_{13} + 1) \cdot R_E\right) \cdot \Delta i \qquad 2.82$$

et

$$\Delta i_0 = -(\beta_{11} + 1) \cdot (\beta_{13} + 1) \cdot \Delta i$$

2.83

Après avoir négliger

$$\frac{1}{g_{BE11}}$$

face à  $\frac{1}{g_{CE7}} / / \frac{1}{g_{CE9}}$ , et  $\frac{1}{g_{BE13}}$  face à  $(\frac{1}{g_{CE7}} / / \frac{1}{g_{CE9}}) \cdot \frac{1}{1 + \beta_{11}}$ , on obtient

$$R_0 = \frac{\Delta u_0}{\Delta i_0} = \left(\frac{1}{g_{CE7}} / / \frac{1}{g_{CE9}}\right) \cdot \frac{1}{(\beta_{11} + 1) \cdot (\beta_{13} + 1)} + R_E$$

2.84

avec

$$\frac{1}{g_{CE7}} = \frac{U_{a(Q7)} + U_{CE0(Q7)}}{I_{C0(Q7)}} = \frac{120 + 15.5}{4.72} = 28708\Omega$$

$$\frac{1}{g_{CE9}} = \frac{U_{a(Q9)} + U_{CE0(Q9)}}{I_{C0(Q7)}} = \frac{120 + 17.8}{4.72} = 29194\Omega$$

2.85

L'impédance de sortie vaut donc

$$R_0 = \frac{\Delta u_0}{\Delta i_0} = \left(\frac{28708 \cdot 29194}{28708 + 29194}\right) \cdot \frac{1}{(150 + 1) \cdot (50 + 1)} + 0.82 = 2.7\Omega$$

2.86

Selon la théorie de la réaction négative non idéale, l'amplificateur peut être décrit sous la forme de la Figure 2-14

Figure 2-14 : Structure de l'amplificateur de tension

et après mise en forme

Figure 2-15 : Structure standard (réaction negative idéale) de l'amplificateur de tension

L'impédance d'entrée du quadripôle A'<sub>V</sub> modifié est définie comme

$$R'_{i} = R_{i} + R_{2} // R_{3}$$

2.87

et l'impédance d'entrée en boucle fermée

$$R'_{iF} = (1 + \beta_V \cdot A'_V) \cdot R'_i$$

2.88

La relation entre u'i et ui s'exprime sous la forme

$$u'_{i} = \frac{R_{i} + R_{2} // R_{3}}{R_{i}} \cdot u_{i} = \frac{R'_{i}}{R_{i}} \cdot u_{i}$$

2.89

L'impédance de sortie du quadripôle modifié s'exprime par la relation

$$R'_{0} = R_{0} / (R_{2} + R_{3}) / R_{L}$$

2.90

et l'impédance en boucle fermée

$$R'_{0F} = \frac{R'_{0}}{(1 + \beta_{V} \cdot A'_{V})}$$

2.91

et l'amplification de tension

$$A'_{V} = \frac{R'_{0}}{R_{0}} \cdot \frac{R_{i}}{R'_{i}} \cdot A_{V}$$

$$2.92$$

Application numérique

$$R'_{i} = 3305 + \frac{1.15}{1.15} \cdot 10^{3} = 4242\Omega$$

$$R'_{0} = \frac{1}{\frac{1}{2.7} + \frac{1}{16 \cdot 10^{3}} + \frac{1}{6.8}} = 1.9\Omega$$

2.94

$$A'_{V} = \frac{3305}{4242} \cdot \frac{1.9}{2.7} \cdot 210450 = 115382 \tag{101dB}$$

$$R'_{iF} = (1 + \frac{1}{16} \cdot 115382) \cdot 4242 = 30M\Omega$$

2.96

$$R'_{0F} = \frac{1.9}{(1 + \frac{1}{16} \cdot 115382)} = 0.26m\Omega$$

2.97

$$A'_{VF} = \frac{115382}{1 + \frac{1}{16} \cdot 115382} = 16 \tag{24dB}$$

#### CONCLUSIONS.

Vu la forte dispersion des paramètres propres à chaque composant, il est important de rester prudent quant aux résultats de la simulation et des mesures effectuées au laboratoire. On peut d'ores et déjà faire les remarques suivantes :

- 1. Le gain en tension de l'étage driver en boucle ouverte (sans charge) est directement fonction des conductances g<sub>CE7</sub> et g<sub>CE9</sub> (voir relation 2.60). Ces conductances, calculée à l'aide de la tension de Early et du courant de collecteur ont des valeurs avec faible dispersion En conséquence le calcul du gain de cet étage est entaché d'une erreur relativement faible.

- 2. Le gain en tension de l'étage différentiel est directement dépendant de l'impédance de charge de ce dernier. Cette impédance de charge correspond à l'impédance d'entrée de l'étage driver, c'est-à-dire 1/g<sub>BE9</sub>. Le calcul de la conductance g<sub>BE9</sub> est peu précis puisque cette conductance dépend de β<sub>9</sub>, grandeur présentant une forte dispersion.

- 3. Vu la valeur de l'impédance d'entrée en boucle fermée, le choix de  $15k\Omega$  pour  $R_1$  assure le respect des spécifications.

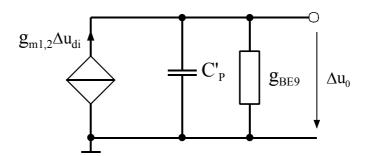

## 2.2 CAPACITÉ DE COMPENSATION C<sub>P</sub>

#### 2.2.1 Introduction

Pour le calcul du gain en tension de l'amplificateur, nous avons utilisé un modèle simplifié (DC) pour les transistors. En effet ce modèle ne tient pas compte des capacités parasites propres à tous les semiconducteurs. En principe, aux basses fréquences (quelques kHz), la simplification que nous avons effectuée ne porte pas à conséquence. Par contre l'adjonction d'une capacité de compensation  $C_p$  entre l'entrée et la sortie de l'étage driver provoque une forte diminution du gain de l'étage différentiel aux basses fréquences déjà.

## 2.2.2 Modification de l'impédance d'entrée de l'étage différentiel

Selon le théorème de Miller, la capacité C<sub>p</sub> rapportée à l'entrée de l'étage driver vaut

$$C_{p}' = C_{p} \cdot (1 - A_{V2})$$

2.99

avec  $A_{V2}$  =-2608 gain du l'étage driver.

Dans ce cas, le schéma par accroissement de l'étage différentiel (voir Figure 2-10) prend la forme suivante

Figure 2-16 : Etage différentiel : Schéma pour accroissement

Le gain en tension devient

$$A_{V3} = \frac{\Delta u_0}{\Delta u_{id}} = g_{m1,2} \frac{1}{g_{BE9}} \cdot \frac{1}{1 + s \cdot \frac{C_P}{g_{BE9}}}$$

2.100

La relation 2.100 met en évidence l'apparition d'un pôle. La fonction de transfert est donc celle d'un passe-bas. En admettant une capacité de compensation  $C_P$  de 470pF, et sachant que  $1/g_{BE9}$  vaut  $547\Omega$  (voir relation 2.67 la pulsation de coupure est de

$$f_C = \frac{1}{2\pi} \omega_C = \frac{1}{2\pi} \frac{g_{BE9}}{C_P'} \cong \frac{1}{2\pi} \frac{g_{BE9}}{(1 - A_{v3}) \cdot C_p}$$

$$= \frac{1}{2\pi} \frac{1}{826 \cdot 2608 \cdot 470 \cdot 10^{-12}} = 157 Hz$$

2.101

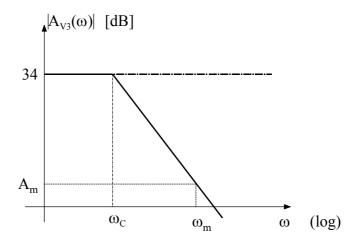

La Figure 2-17 illustre la fonction de transfert liée au gain en tension de l'étage différentiel

Figure 2-17 : Etage différentiel : Gain en tension

Une mesure du gain de l'étage différentiel à la fréquence  $f_m=10 kHz$  par exemple nous donne un gain  $A_m$  fortement réduit.

$$|A_m| = A_{V3} \cdot \frac{1}{\sqrt{1 + \left(\frac{f_m}{f_C}\right)^2}} \cong A_{V3} \frac{f_C}{f_m} = 75 \frac{157}{10000} = 1.31$$

$$2.102$$

## 2.3 CONCLUSION

En guise de conclusion, la mesure du gain de l'étage différentiel  $A_{V3}$  doit se faire à une fréquence de l'ordre de 10Hz si on veut faire une comparaison calcul – mesure.